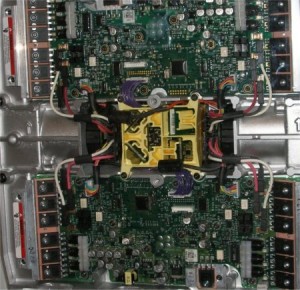

Vi tager en lille gætteleg her. Hvilket “revolutionerende” apparat stammer det her billede fra?

Kategori: ‘Brainer’

Brainer: Hvor er kortslutningen?

Den er simpel denne gang: Printet kommer retur fra montage. Det er første prototype. Du får 5 monterede print – men på det ene er der en kortslutning et sted, så der ikke kan komme spænding på et af power planerne.

Løsning: Nu med C

Løsning: CLK net

Brainer: Nu med C

Morten påstår at han aldrig ville have skrevet det her kode sådan ![]()

Der er indtil flere ting galt. Du finder garanteret hurtigt det, der har med performance at gøre; men der er faktisk en detalje, der gør, at det en sjælden gang imellem ikke vil virke. Hvilken?

Brainer: CLK net

Forestil dig at du som det sidste kvalitetscheck og gennemgang af dine log filer får øje på denne besked (her fra et Xilinx compile): (mere…)

Brainer: ADC clock

Her kommer vanen tro en lille udfordring med lidt hovedbrud til FPGA folket. Den stammer fra et projekt, hvor det nok er nemmest at forestille sig et “hovedkort” med en FPGA på, som kan kobles sammen med to forskellige “indstikskort” med A/D convertere på. Det første indstikskort går fint nok – der skal samles serielle data op på rising edge: (mere…)

Brainer: SignalTap mystik

Baggrunden er en anden case fra et kundeprojekt, hvor Alex fejlsøgte på et kredsløb. Den simple kode til testen er her – men se på output fra SignalTap…