Tag ‘signal-integritet’

Normal laver vi elektronik baseret på en kravspecifikation. Men hvad hvis kravene kun findes i form af et gammelt eksisterende system? Så må man karakterisere systemet, gennemgå dokumentation og sammenligne med virkeligheden. Og når man så mener at have forstået opgaven må man overveje hver enkelt del: Skal det grundlæggende design beholdes eller er det nemmere at designe det forfra?

Normal laver vi elektronik baseret på en kravspecifikation. Men hvad hvis kravene kun findes i form af et gammelt eksisterende system? Så må man karakterisere systemet, gennemgå dokumentation og sammenligne med virkeligheden. Og når man så mener at have forstået opgaven må man overveje hver enkelt del: Skal det grundlæggende design beholdes eller er det nemmere at designe det forfra?

If it works – don’t fix it… Not. Det gælder ikke ingeniører. Ingeniører, jeg kender, ynder at splitte ting ad der virker, blot for at konstatere hvordan teknologien er samlet til et fungerende hele. (mere…)

Tags: analog, digitalelektronik, hardware, i/o, innovation, RF, signal-integritet

Posted in Case, Debat, Nyheder, Teknologi | No Comments »

Processorer sidder i snart sagt alt. Men hvordan skal kagen skæres? Skal CPU’en ind i en FPGA, skal der være en DSP, alt på en chip eller uafhængige systemer. Den seneste udvikling for SoC FPGA’er prøver at skubbe til balancen.

Processorer sidder i snart sagt alt. Men hvordan skal kagen skæres? Skal CPU’en ind i en FPGA, skal der være en DSP, alt på en chip eller uafhængige systemer. Den seneste udvikling for SoC FPGA’er prøver at skubbe til balancen.

I sin grundsubstans er der ikke så meget nyt indenfor SoC devices fra FPGA leverandørerne. I årevis er der bygget systemer med CPU funktionalitet trukket ind i FPGAerne, og teknologien har været moden længe. Vi har utallige gange været igennem systemovervejelser, hvor netop fordele og ulemper med diskret processorsystem er blevet sammenlignet med processorsystemer indlejret i FPGA. Vi har ofte været stillet opgaven med at evaluere de forskellige løsninger mht. omkostninger, ydelse og fleksibilitet. (mere…)

Tags: altera, digitalelektronik, FPGA, hardware, si, signal-integritet, SoC, software, VHDL, Xilinx

Posted in Case, Teknologi | No Comments »

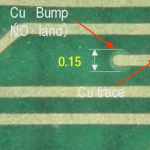

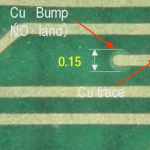

HDI (High-Density-Interconnect) som begreb er en anelse flydende,

Padless via (foto: Mr. Holden).

men vi anser det som fællesbetegnelsen for printkort, som har høj konnektivitet gennem ofte begravede laser via’er og små geometrier under anvendelse af specielle materialer.

Igennem mange år har vi slået et slag for, at power og signal integriteten er en vigtig del af en elektrisk konstruktion. Printpladerne er en vigtig brik i dette spil, da impedanser og forsyningsnetværk i høj grad defineres af printpladerne konstruktion. Denne tilgang til printplade design har i høj grad været drevet af elektronikkens behov. Hvad sker der egentlig, hvis vi tager udgangspunkt i printet for at vurdere, hvad printet kan tilbyde for elektronikken frem for at fokusere på, hvad elektronikken kræver af printet.

(mere…)

Tags: digitalelektronik, hardware, PCB, PDN, prototype, signal-integritet

Posted in Nyheder, Process, Teknologi | No Comments »

Når man skal sample noget, hvad enten det er et digitalt eller analogt signal, har man brug for en stabil clock. Da mange systemer reagerer på flanken og stige/falde tider typisk er nogenlunde konstante, fokuserer man især på ”vandret støj”, dvs. i tidsaksen.  Der er mange definitioner og målemetoder, og der er, specielt i telecom verdenen, en masse metoder for at håndtere dette. Disse kan være nok så indviklede; men i det mindste er de relevante data og metoder ofte tilgængelige. Denne artikel skal derfor mere handle om, hvad man gør, når man bliver mødt med et, ofte meget upræcist, krav til sin clock. (mere…)

Der er mange definitioner og målemetoder, og der er, specielt i telecom verdenen, en masse metoder for at håndtere dette. Disse kan være nok så indviklede; men i det mindste er de relevante data og metoder ofte tilgængelige. Denne artikel skal derfor mere handle om, hvad man gør, når man bliver mødt med et, ofte meget upræcist, krav til sin clock. (mere…)

Tags: ADC, analog, digitalelektronik, FPGA, hardware, signal-integritet, timing

Posted in Debat, Nyheder, Teknologi | No Comments »

Der har efterhånden været hype omkring fysiske 3D modeller i et stykke tid. Mange virksomheder er gået helt om bord i 3D-printere med det formål tidligt at kunne kvalificere mekaniske konstruktioner og integration med systemer og ikke mindst tests hos brugerne.  For den indlejrede elektronik er 3D print af konstruktionerne med til at afluse problemer med byggehøjder, fejlplacerede skruehuller osv. MEN – hvad med udstråling, crosstalk og EMI. Hvad gør vi med det? En kunststof model af vores printplader giver jo ikke just mulighed for at måle udstråling, udbredelse af strømme på printet, etc. En tur i testlab viser, at grænseværdier ikke bliver overholdt. De kreative løsninger kommer på bordet. Blandinger af feritter og skærmende kasser/tape kan nogle gange være med til at indkapsle problemet og måske spare et re-spin.

For den indlejrede elektronik er 3D print af konstruktionerne med til at afluse problemer med byggehøjder, fejlplacerede skruehuller osv. MEN – hvad med udstråling, crosstalk og EMI. Hvad gør vi med det? En kunststof model af vores printplader giver jo ikke just mulighed for at måle udstråling, udbredelse af strømme på printet, etc. En tur i testlab viser, at grænseværdier ikke bliver overholdt. De kreative løsninger kommer på bordet. Blandinger af feritter og skærmende kasser/tape kan nogle gange være med til at indkapsle problemet og måske spare et re-spin.

Udfordringen er at omkostningerne, der fremkommer som følge af re-spin(s) af konstruktionen og af den medfølgende forsinkelse, er betydelige. Når vi først står i testlab, så er udviklingsprojektet “så godt som færdigt”, og både budget og kalendertid er brugt. Salgsteamet har allerede den første kunde som skriger på produktet.

(mere…)

Tags: EMC, EMI, hardware, prototype, signal-integritet, simulering, troubleshooting

Posted in Debat | No Comments »

Vi gentager og udvider hermed en opfordring til at deltage i ERFA grupper indenfor FPGA og Signal Integrity. Vi samler kandidater sammen.

For nogle måneder siden inviterede vi til et forum for åben sparring mellem FPGA kyndige. Formålet er, at vi på tværs i industrien skal have en mulighed for at hjælpe hinanden til øget viden og netværk. Vi har fået positivt feedback på ideen, og fra flere sider er der opbakning til, at vi samler trådende, da vi har fat i mange udviklere på tværs af industrien.

Vi følger derfor op på idéen med en ERFA gruppe for Signal Integrity.

Vi vil gerne have flere lokket ud af busken og opfordrer derfor til, at hvis du selv er erfaren FPGA eller SI-mand, eller kender en som er det, så skyd en email til os.

(mere…)

Tags: ERFA, erfagruppe, FPGA, signal-integritet

Posted in Debat | No Comments »

Når lab ligger i nærheden af London, kan adgangen til faciliteterne være lidt bøvlede, når der er mange tusinde atleter og sportsinteresserede, som er rykket til London og omegn. Det måtte vi i hvert fald sande, da vi i løbet af sommeren gerne skulle forbi et lab for at få kvalificerede målinger på vores seneste design med 8 FPGAer bundet sammen med giga-bit links. Missionen var at se, om vi havde regnet og simuleret rigtigt og at de print, vi efterfølgende havde fået produceret, var af den fornødne kvalitet. Der var nemlig lidt mystik over link kvaliteten, som var svær at få indkredset uden lettere eksotiske måleinstrumenter.

(mere…)

Tags: digitalelektronik, hardware, prototype, signal-integritet

Posted in Nyheder | No Comments »

Normal laver vi elektronik baseret på en kravspecifikation. Men hvad hvis kravene kun findes i form af et gammelt eksisterende system? Så må man karakterisere systemet, gennemgå dokumentation og sammenligne med virkeligheden. Og når man så mener at have forstået opgaven må man overveje hver enkelt del: Skal det grundlæggende design beholdes eller er det nemmere at designe det forfra?

Normal laver vi elektronik baseret på en kravspecifikation. Men hvad hvis kravene kun findes i form af et gammelt eksisterende system? Så må man karakterisere systemet, gennemgå dokumentation og sammenligne med virkeligheden. Og når man så mener at have forstået opgaven må man overveje hver enkelt del: Skal det grundlæggende design beholdes eller er det nemmere at designe det forfra?

Der er mange definitioner og målemetoder, og der er, specielt i telecom verdenen, en masse metoder for at håndtere dette. Disse kan være nok så indviklede; men i det mindste er de relevante data og metoder ofte tilgængelige. Denne artikel skal derfor mere handle om, hvad man gør, når man bliver mødt med et, ofte meget upræcist, krav til sin clock.

Der er mange definitioner og målemetoder, og der er, specielt i telecom verdenen, en masse metoder for at håndtere dette. Disse kan være nok så indviklede; men i det mindste er de relevante data og metoder ofte tilgængelige. Denne artikel skal derfor mere handle om, hvad man gør, når man bliver mødt med et, ofte meget upræcist, krav til sin clock.  For den indlejrede elektronik er 3D print af konstruktionerne med til at afluse problemer med byggehøjder, fejlplacerede skruehuller osv. MEN – hvad med udstråling, crosstalk og EMI. Hvad gør vi med det? En kunststof model af vores printplader giver jo ikke just mulighed for at måle udstråling, udbredelse af strømme på printet, etc. En tur i testlab viser, at grænseværdier ikke bliver overholdt. De kreative løsninger kommer på bordet. Blandinger af feritter og skærmende kasser/tape kan nogle gange være med til at indkapsle problemet og måske spare et re-spin.

For den indlejrede elektronik er 3D print af konstruktionerne med til at afluse problemer med byggehøjder, fejlplacerede skruehuller osv. MEN – hvad med udstråling, crosstalk og EMI. Hvad gør vi med det? En kunststof model af vores printplader giver jo ikke just mulighed for at måle udstråling, udbredelse af strømme på printet, etc. En tur i testlab viser, at grænseværdier ikke bliver overholdt. De kreative løsninger kommer på bordet. Blandinger af feritter og skærmende kasser/tape kan nogle gange være med til at indkapsle problemet og måske spare et re-spin.