Byg et array med 16 Xilinx Virtex FPGA’er og 32 A/D konvertere med nok båndbredde så alle 16 FPGA’er kan modtage alle data fra A/D konverterne.

Gør det hurtigt! Og der skal kun bygges 2-3 systemer.

Og glemte jeg at specificere A/D konverterne? Ok: 10 MSa/s i 14 bit.

Så simpelt kan opgaven beskrives. Hvor svært kan det være? Lad os se på det…

Båndbredde

32 x 10 MSa/s x 14 bit ~4.5 Gbit/s

Så bygger vi med 3.125 Gbps RocketIO, skal vi have 2 links per FPGA.

Topologi

Det er vist nemmest med en tegning her.

Alle links er 3.125 Gbps serielle links. De røde går i kabler, mens de blå er routet i printkortet.

Alle links er 3.125 Gbps serielle links. De røde går i kabler, mens de blå er routet i printkortet.

Der kom også lige 2 x 1G ethernet links på den ene FPGA, så data kan komme ud af systemet efter processering.

Hardware i moduler

Så simpelt kan systemet bygges. Hver af de 4 stiplede firkanter med 4 FPGA’er er et Sundance “carrier board”. Det ser sådan her ud:

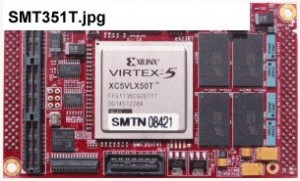

Vi monterer 4 FPGA moduler på hver carrier board. Vi kan f.eks. vælge det her modul med Virtex-5 SX95T, som også har 2 GB DDR-II ekstern RAM:

Vi monterer 4 FPGA moduler på hver carrier board. Vi kan f.eks. vælge det her modul med Virtex-5 SX95T, som også har 2 GB DDR-II ekstern RAM:

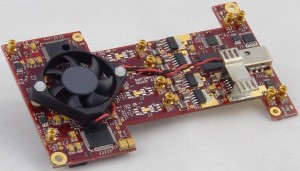

Oven på 8 af de 16 FPGA moduler kan vi placere et 4-kanal ADC modul. På den måde får vi 32 A/D kanaler:

Så har vi hardwaren på plads. Der mangler måske lige en standard strømforsying og et passende chassis.

Så har vi hardwaren på plads. Der mangler måske lige en standard strømforsying og et passende chassis.

Det er svært at vise et billede, da systemet ikke er bygget endnu – men her er et helt andet system opbygget på en tilsvarrende måde:

Det skulle give ideen. Det kan gøres lidt mere elegant, men afhængig af formålet kan være fint nok sådan.

Det skulle give ideen. Det kan gøres lidt mere elegant, men afhængig af formålet kan være fint nok sådan.

Det er vigtigt at sørge for køling, da et så kraftigt system vil bruge meget strøm og kræve meget køling. Det er ikke helt trivielt, men kan gøres med passende blæsere, hvilket er acceptabelt i denne situation.

Konfiguration

Så stort et FPGA array skal også kunne konfigureres. Og gerne effektivt, så udviklerene af de algoritmer, som skal køre derpå ikke behøver bekymre sig om hardware detaljer. Der skal faktisk bruges en art “OS” eller “HAL” (Hardware Abstraction Layer). Det findes der en meget fin løsning på, i noget som hedder Diamond FPGA fra den skotske virksomhed 3L. Det må blive et emne for et andet indlæg. Update: Læs mere om configuration her.

Hvad koster det?

Slag på tasken – det viste system kan bygges for lige over 1 Mkr per system og være klar til brug på under 2 måneder.

Skulle man ikke hellere udvikle custom FPGA boards til formålet, så man kan gøre det endnu billigere? Nej – det kunne være sjovere – men ikke særlig fornuftigt set i et pris/risiko perspektiv. Det ville desuden væsentligt forsinke projektet, hvorved erfaringer og resultater først ville kunne høstes langt senere i forløbet.

Vi hører at DTU Elektro i et projekt med bla. Rigshospitalet har bestilt et lignende system – dog med 64 x 5 FPGA’er. Altså 20x så stort, som det system der er beskrevet her. Det projekt er efter års arbejde kommet så langt, at et printkort med 5 FPGA’er fungerer nogenlunde stabilt (resultat netop fremlagt på en temadag i IDA regi). Det kunne være interessant at vide, hvor stor glæde DTU Elektro og Rigshospitalet ville have haft af en væsentlig hurtigere og mere sikker udvikling som beskrevet ovenfor…

Det projekt er bla. omtalt af Version 2 på http://www.version2.dk/artikel/7705-verdens-hurtigeste-realtidscomputer-er-dansk