At få konfigureret en FPGA er altid en del af udfordringen. Skal vi bygge et multi-FPGA system, som det “reconfigurable computing FPGA array” med mange FPGA’er vi beskrev tidligere – så er det bare endnu mere besværligt.

Et FPGA array er en specialiseret super-computer. De algoritmer, som skal køre på den, bør ideelt set skrives helt generisk uden at tage hensyn til den detaljerede hardware arkitektur.

Vi skal have et hardware abstraction layer (HAL).

På den måde kan de, som udvikler algoritmerne fokusere 100% på algorimter og lade automatikken håndtere både FPGA configuration og hardware detaljer. Detaljer som hvordan de forskellige dele af algoritmerne er forbundet, hvilken fysisk FPGA de kører på osv.

Det er præcis hvad skotske 3L kan med deres Diamond FPGA tool…

Lad os se hvordan det kan bruges til vores reconfigurable FPGA array.

Algoritmen

Meget simpelt forklaret kan algoritmen beskrives som to “tasks” (vi bruger termen “tasks” for VHDL kode som genererer en strøm af output på basis af en strøm af input – meget simpelt). Vi kalder de to tasks for A og B:

Så vi har 31 kopier af Task A+B. Og en kopi med en ekstra task, som håndterer 1G ethernet for output. Desuden er der en ADC Task som håndterer opsætning af A/D konverteren og spytter data ud i en lind strøm (14 bit @ 10 MSa/s).

Så vi har 31 kopier af Task A+B. Og en kopi med en ekstra task, som håndterer 1G ethernet for output. Desuden er der en ADC Task som håndterer opsætning af A/D konverteren og spytter data ud i en lind strøm (14 bit @ 10 MSa/s).

Ideen er:

- Data fra de 32 A/D konvertere sendes til alle A tasks.

- Hver task A har en “partner task” B, som den kommunikerer med (lav båndbredde). Task B kan være placeret på en anden FPGA.

- Resultatet fra algoritmen samles fra de 32 stk Task A i GigE boblen, hvor det sendes ud over en eller to 1G ethernet forbindelser.

Med Diamond FPGA kan de tre tasks A, B og GigE kan skrives som 100% generisk VHDL. Det eneste krav er, at de følger en meget simpel model for generisk input/output med en 32 bit bus og et sæt af handshake signaler.

Diamond FPGA kører hele processen i samarbejde med Xilinx ISE synteseværktøjet, som faktisk er integreret ind i Diamond FPGA’s IDE under Eclipse.

Mapping

Kort beskrevet kan Diamond FPGA mappe et logisk, 100% generisk, hardwareuafhængigt VHDL design som vist her:

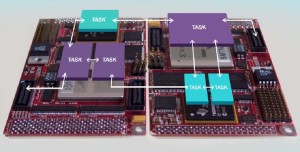

Toolet mapper et generisk design til den fysiske hardware, som illusteret her:

Toolet mapper et generisk design til den fysiske hardware, som illusteret her:

Magien som foregår i toolet er simpel, men utrolig værdifuld i et FPGA array, hvor du som bruger ønsker at fokusere på udvikling af algoritmer – ikke på hardware afhængigheder.

Jeg håber dette beskriver hvordan kombinationen af 3L’s Diamond FPGA og Sundance moduler med FPGA, DSP og AD/DA gør det meget nemt at bygge og ikke mindst bruge selv ganske store systemer med mange FPGA’er. Og det hele kan gøres meget hurtigt baseret på hyldevarer.